- 7.1 簡介

- 7.2 串入串出移位暫存器

- 7.3 串入並出移位暫存器

- 7.4 並入串出移位暫存器

- 7.5 並入並出移位暫存器

在 6.4 節我們曾提及,一個 m 位元的暫存器可由 m 個 D 型正反器連接而成,用來儲存 m 個位元的資料 (參見圖 6.34)。移位暫存器是一種廣泛應用於數位電路設計中的特殊暫存器,本章將詳細介紹其中最常用的四種,分別是:串入串出移位暫存器、串入並出移位暫存器、並入串出移位暫存器、並入並出移位暫存器。這四種暫存器的名稱是依照輸入資料的位元數目和輸出資料的位元數目來區別的。如果一次僅有一個位元輸入電路中,則稱為「串入」(serial in);若一次多個位元一起輸入電路中,則稱之為並入 (parallel in)。同理,一次僅有一個位元從電路中輸出,則稱串出 (serial out);若多個位元一起輸出,則稱之為並出 (parallel out)。此外,這四種暫存器在結構上都屬於 D型正反器的串接,而內部資料的轉移則是一次一個位元 (即一個時鐘脈衝一個位元)。在接下來的四個小節中,我們將依序介紹這些暫存器。

Copyright©滄海書局

## 7.2 串入串出移位暫存器

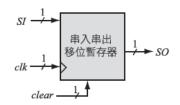

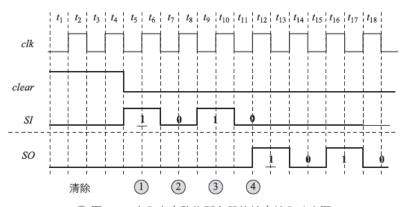

串入串出移位暫存器 (serial in serial out shift register, SISO) 有三個單位元的輸入,分別為:串列輸入 (SI)、時鐘脈衝 (clk) 以及清除 (clear) 位元 (清除位元和前一章的重置位元功用完全相同);其輸出則是單位元的串列輸出 (SO)。其方塊圖如圖 7.1 所示。

◎ 圖 7.1 串入串出移位暫存器方塊圖

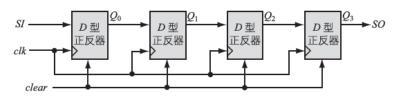

◎ 圖 7.2 四位元串入串出移位暫存器內部結構圖

一個四位元的串入串出移位暫存器的內部結構圖如圖 7.2 所示,由四個正緣觸發 D型正反器串接構成,前一個正反器的輸出連接到下一個正反器的輸入。

Copyright©滄海書局

圖中,串列輸入訊號從最左邊的正反器進入移位暫存器中,而串 列輸出訊號則是儲存在最右邊正反器中。此移位暫存器的行為說明如 下:

- (1) 只要 clear 訊號為 1,所有正反器會被清除為 0 (此為非同步清除)。

- 當時脈輸入訊號 (clk) 的正緣到達時,電路開始進行移位,因為所有的正反器同時被 clk 觸發,所以四個正反器會在同一時刻各自把左邊的輸入資料存入其內部 (即正緣到達瞬間, $SI \to Q0(t) \cdot Q0(t-1) \to Q1(t) \cdot Q1(t-1) \to Q2(t) \cdot Q2(t-1) \to Q3(t)$ ,這四個動作同步執行),就如同正反器的資料同時往

- → Q3(t),這四個動作同步執行),就如同正反器的資料同時往右傳遞一個正反器 (右移 1 個位元) 一樣。如此一來,輸入資料 SI 是從最左邊的正反器一位元一位元地進入電路中,最右邊正 反器的輸出位元資料,會被當作整個移位暫存器電路的串列輸出訊號 (SO = Q3)。

(2) 若 clear 為 0, 其電路動作為:

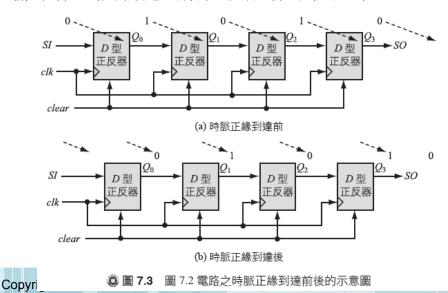

圖 7.3 是一個完整的例子,呈現如圖 7.2 四位元串入串出移位暫存器的時脈正緣到達前之原始輸入值及時脈正緣到達後每一個正反器所輸出的值,很明顯地,所有正反器的值右移了一位。

由於每個時脈正緣只能輸入與輸出 1 個位元的資料,所以是一種傳輸速率較慢的移位暫存器。此外,這個四位元移位暫存器,在每一個時脈正緣時會右移一個資料位元,所以經過四個時脈正緣後,在 SI 輸入的位元會右移到 SO。如果忽略正反器的閘傳遞延遲,則此電路的時序圖如圖 7.4 所示。

◎ 圖 7.4 串入串出移位暫存器的輸出輸入時序圖

圖中,在時段  $t1\sim t4$ ,clear = 1,所以全部的正反器清除為 0。之後,clear = 0,電路開始動作。

在時段 t5~t6 間,clk 的正緣到達時,全部的正反器開始移位,目前 Sl 值 1 存入最左邊的暫存器。時段 t7~t8 間 clk 的正緣到達時,全部的正反器再次右移一位,新 Sl 值 0 存入最左邊的暫存器。時段 t9~t10間 clk 的正緣到達時,全部的正反器再次右移一位,新 Sl 值 1 存入最左邊的暫存器。時段 t11~t12 間 clk 的正緣到達時,再次右移一位,新 Sl 值 0 存入最左邊的暫存器,同時在四個週期之前所輸入的 Sl 值 (標示為 1) 已經到達輸出 SO 端,開始順利輸出。之後的每個時脈正緣,資料將會持續右移。圖中四個圓圈數字 (標示 1~4),則表示第一筆 Sl 輸入資料傳遞到移位暫存器輸出端所需的四個時脈正緣。

Copyright©滄海書局

## 7.3 串入並出移位暫存器

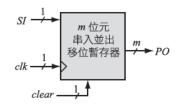

串入並出移位暫存器 (serial in parallel out shift register, SIPO) 有三個單位元的輸入,分別為:串列輸入 (SI)、時鐘脈衝 (clk) 以及清除 (clear) 位元;其輸出則是全部 m 位元的並列輸出 (PO)。圖 7.5 是一個 m 位元的串入並出移位暫存器之方塊圖。

◎ 圖 7.5 m 位元串入並出移位暫存器方塊圖

一個四位元的串入並出移位暫存器的內部結構圖如圖 7.6 所示,由四個正緣觸發 D型正反器串接構成,前一個正反器的輸出連接到下一個正反器的輸入。

◎ 圖 7.6 四位元串入並出移位暫存器內部結構圖

Copyright©滄海書局

圖中,串列輸入訊號從最左邊的正反器進入移位暫存器中,而並列輸出訊號則是從全部的正反器一起讀出(即 PO3 = Q3、PO2 = Q2、

$PO1 = Q1 \cdot PO0 = Q0)$ 。此移位暫存器的行為說明如下:

(1) 只要 clear 訊號為 1,所有正反器會被清除為 0 (此為非同步清除)。

(2) 若 clear 為 0, 其電路動作為:

當時脈輸入訊號 (clk) 的正緣到達時,電路開始進行移位,因為所有的正反器同時被 clk 觸發,所以四個正反器會在同一時刻各自把左邊的輸入資料存入其內部 (即正緣到達瞬間, $SI \rightarrow Q0(t) \times Q0(t-1) \rightarrow Q1(t) \times Q1(t-1) \rightarrow Q2(t) \times Q2(t-1)$

→ Q3(t),這四個動作同步執行),就如同正反器的資料同時往 右傳遞一個正反器 (右移 1 個位元) 一樣。輸入資料 SI 是從最 左邊的正反器一位元一位元地進入電路中,每個正反器貢獻一 位元的輸出資料,所以四位元的 PO0PO1PO2PO3 同時從電路輸 出外部。

每個時脈正緣只能輸入一個位元的資料,但是會同時輸出四位元 的資料。此類型的移位暫存器通常用來接收串列輸入並轉換成為並列 輸出。

Copyright©滄海書局

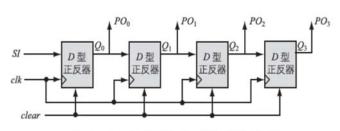

◎ 圖 7.7 四位元串入並出移位暫存器的輸出輸入時序圖

四位元串入並出移位暫存器在每一個時脈正緣時,會右移一個資料位元,所以經過四個時脈正緣後,在 SI 輸入的位元會右移到 PO3。

如果忽略正反器的閘傳遞延遲,則此電路的時序圖如圖 7.7 所示。

Copyright©滄海書局

圖中,在時段  $t1\sim t4$ ,clear=1,所以全部的正反器清除為 0。之 後,clear=0,電路開始動作。

時段 t5~t6 間 clk 的正緣到達時,全部的正反器開始移位,目前 Sl 值 1 存入最左邊的暫存器,此時四位元輸出從左到右為 1000。時段 t7~t8 間 clk 的正緣到達時,全部的正反器再次右移一位,新 Sl 值 0 存入最左邊的暫存器,此時四位元輸出從左到右為 0100。時段 t9~t10 間 clk 的正緣到達時,全部的正反器再次右移一位,新 Sl 值 1 存入最左邊的暫存器,此時四位元輸出從左到右為 1010。時段 t11~t12 間 clk 的正緣到達時,再次右移一位,新 Sl 值 0 存入最左邊的暫存器,此時四位元輸出從左到右為 1010。時段 t11~t12 間 clk 的正緣到達時,再次右移一位,新 Sl 值 0 存入最左邊的暫存器,此時四位元輸出從左到右為 0101,在四個週期之前所輸入的 Sl 值 (標示為 1)已經右移到達輸出 PO3。之後的每個時脈正緣,資料將會持續右移。圖中四個圓圈數字 (標示 1~4),則表示第一筆 Sl 輸入資料傳遞到移位暫存器輸出 PO3 端所需的四個時脈正緣。

## 7.4 並入串出移位暫存器

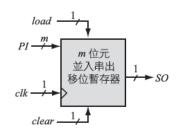

並入串出移位暫存器 (parallel in serial out shift register, PISO) 的輸入包含:時鐘脈衝 (clk) 位元、清除 (clear) 位元、載入 (load) 位元以及 m 位元並列輸入 (PI);其輸出則是單位元的串列輸出 (SO)。圖 7.8是一個 m 位元的並入串出移位暫存器之方塊圖。

◎ 圖 7.8 m 位元並入串出移位暫存器方塊圖

Copyright©滄海書局

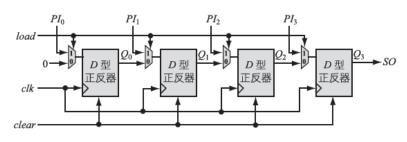

一個四位元的並入串出移位暫存器的內部結構圖如圖 7.9 所示,由四個正緣觸發 D型正反器串接構成,前一個正反器的輸出連接到下一個正反器的輸入。

◎ 圖 7.9 四位元並入串出移位暫存器內部結構圖

圖中,四位元並列輸入訊號會同時進入各自的正反器中,而串列 輸出訊號則是依序一位元一位元從最後一個正反器輸出。此移位暫存 器的行為說明如下:

- (1) 只要 clear 訊號為 1,所有正反器會被清除為 0 (此為非同步清除)。

- (2) 若 clear 為 0, 其電路動作為:

- **a.** 當 *load* 為 1,時脈正緣 *clk* 到達時,會將四位元的輸入訊號 以並行方式同時載入到四個正反器中 (即正緣到達瞬間,*Pl*0  $\rightarrow$  Q0(t)、*Pl*1  $\rightarrow$  Q1(t)、*Pl*2  $\rightarrow$  Q2(t)、*Pl*3  $\rightarrow$  Q3(t),這四個動 作同步執行)。

- **b.** 當 *load* 為 0,時脈正緣 *clk* 到達時,電路開始進行移位。 因為所有的正反器同時被 *clock* 觸發,所以四個正反器會在同一時刻各自把左邊的輸入資料存入其內部 (即正緣到達瞬間, $0 \to Q0(t) \cdot Q0(t-1) \to Q1(t) \cdot Q1(t-1) \to Q2(t) \cdot Q2(t-1) \to Q3(t)$ ,這四個動作同步執行),就如同正反器的資料同時往右傳遞一個正反器 (右移 1 個位元) 一樣。輸出資料會從最右邊的正反器一位元一位元地輸出電路外部。

在時脈正緣到達時能同時輸入4個位元的資料,但是只會輸出一位元的資料。此類型的移位暫存器通常用來接收並列輸入並轉換成為 中列輸出。

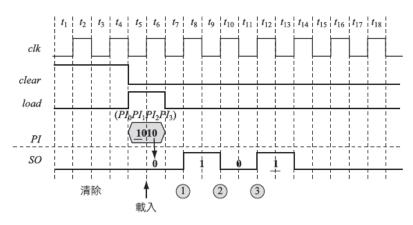

◎ 圖 7.10 四位元並入串出移位暫存器的輸出輸入時序圖

若 load = 1,當時脈正緣到達時,四位元的輸入資料會同時存入四個正反器中。當 load = 0 時,每次時脈正緣到達時,所有正反器的資料都會右移一位。如果忽略正反器的閘傳遞延遲,則此電路的時序圖如圖 7.10 所示。

圖中,在時段 t1~t4,clear = 1,所以全部的正反器清除為 0。之後,clear = 0,電路開始動作。Copyright®滄海書局

時段 t5~t6 間 clk 的正緣到達時,load = 1,所以將四位元的 Pl值 1010 並行載入四個正反器中。此時,最後 (右) 一個正反器的值為 0 (即 Pl3),故輸出 SO 端也是 0。時段 t7~t8 間 clk 的正緣到達時,load = 0,所以全部的正反器右移一位,0 值存入最左邊的暫存器,而最後 (右) 一個正反器的值為 1,故輸出 SO 端也是 1。時段 t9~t10 間 clk 的正緣到達時,全部的正反器再右移一位,0 值存入最左邊的暫存器,而最後 (右) 一個正反器的值為 0,故輸出 SO 端也是 0。時段 t11~t12 間 clk 的正緣到達時,全部的正反器再右移一位,0 值存入最左邊的暫存器,而最後 (右) 一個正反器的值為 1,故輸出 SO 端也是 1。此時,是並行載入四位元輸入資料之後的第三個時脈正緣 (如圓圈數字標示),原始載入最左邊的 Pl0 (標示為 1) 值,已經右移到達輸出 SO。

Copyright©滄海書局

## 7.5 並入並出移位暫存器

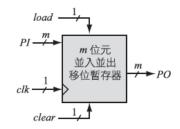

並入並出移位暫存器 (parallel in parallel out shift register, PIPO) 的輸入包含:時鐘脈衝 (clk) 位元、清除 (clear) 位元、載入 (load) 位元以及 m 位元並列輸入 (Pl);其輸出則是 m 位元的並列輸出 (PO)。圖 7.11 是一個 m 位元的並入並出移位暫存器之方塊圖。

◎ 圖 7.11 m 位元並入並出移位暫存器方塊圖

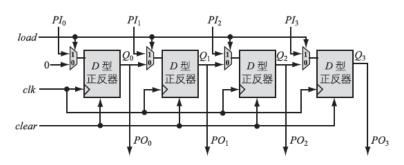

一個四位元的並入並出移位暫存器的內部結構圖如圖 7.12 所示,由四個正緣觸發 D型正反器串接構成,前一個正反器的輸出連接到下一個正反器的輸入。

◎ 圖 7.12 四位元並入並出移位暫存器內部結構圖

Copyright©滄海書局

圖中,四位元並列輸入訊號會同時進入各自的正反器中,而並 列輸出訊號也是同時從四個正反器輸出。此移位暫存器的行為說明如 下:

- (1) 只要 clear 訊號為 1,所有正反器會被清除為 0 (此為非同步清除)。

- (2) 若 clear 為 0, 其電路動作為:

- a. 當 load 為 1,時脈正緣 clk 到達時,會將四位元的輸入訊號 以並行方式同時載入到四個正反器中 (即正緣到達瞬間, $Pl0 \rightarrow Q0(t)$ 、 $Pl1 \rightarrow Q1(t)$ 、 $Pl2 \rightarrow Q2(t)$ 、 $Pl3 \rightarrow Q3(t)$ ,這四個動

作同步執行)。而此時,四個正反器的值也會並行輸出到外部  $Q0(t) \rightarrow PO0 \cdot Q1(t) \rightarrow PO1 \cdot Q2(t) \rightarrow PO2 \cdot Q3(t) \rightarrow PO3$ ,這 四個動作同步執行)。

**b.** 當 *load* 為 **0**,時脈正緣 *clk* 到達時,電路開始進行移位,因為所有的正反器同時被 *clock* 觸發,所以四個正反器會在同一時刻各自把左邊的輸入資料存入其內部 (即正緣到達瞬

間, $0 \rightarrow Q0(t)$ 、 $Q0(t-1) \rightarrow Q1(t)$ 、 $Q1(t-1) \rightarrow Q2(t)$ 、Q2(t-1)

→ Q3(t), 這四個動作同步執行), 就如同正反器的資料同時 往右傳遞一個正反器 (右移 1 個位元) 一樣。同時,四個正反 器資料會並行輸出到電路外部。

電路在時脈正緣能同時輸入 4 個位元的資料且同時輸出 4 個位元的資料。Copyrighte 清海書局

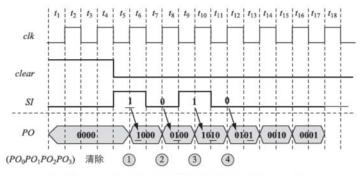

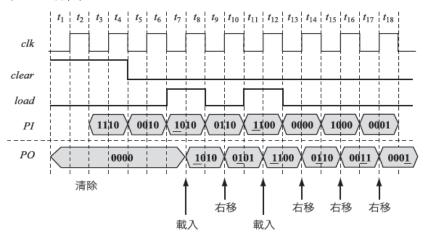

若 load = 1,當時脈正緣到達時,四位元的輸入資料會同時存入四個正反器中。當 load = 0 時,每次時脈正緣到達時,所有正反器的資料都會右移一位。如果忽略正反器的閘傳遞延遲,則此電路的時序圖如圖 7.13 所示。

◎ 圖 7.13 四位元並入並出移位暫存器的輸出輸入時序圖

Copyright©滄海書局

圖中,在時段  $t1 \sim t4$ ,clear = 1,所以全部的正反器清除為 0,故 四位元的 PO 為 0000。之後, clear = 0, 電路開始動作。 時段  $t5\sim t6$  間 clk 的正緣到達時,load = 0,電路執行右移,0 值存 入最左邊的暫存器,故四位元的 PO 還是 0000。時段 t7~t8 間 clk 的正 緣到達時, load = 1, 所以將四位元的 PI 值 1010 並行載入四個正反器 中,故四位元的 PO 是 1010。時段  $t9\sim t10$  間 clk 的正緣到達時,load =0, 電路執行右移, 0 值存入最左邊的暫存器, 其他暫存器右移一位, 故四位元的 PO 是 0101。時段  $t11\sim t12$  間 clk 的正緣到達時,load = 1, 所以將四位元的 PI 值 1100 並行載入四個正反器中,故四位元的 PO 是 1100。時段  $t13\sim t14$  間 clk 的正緣到達時, load=0,電路執行右移, 0 值存入最左邊的暫存器,其他暫存器右移一位,故四位元的 PO 是 0110。時段  $t15 \sim t16$  間 clk 的正緣到達時,load = 0,電路執行右移, 0 值存入最左邊的暫存器,其他暫存器右移一位,故四位元的 PO 是 0011。時段  $t17 \sim t18$  間 clk 的正緣到達時,load = 0,電路執行右移, 0 值存入最左邊的暫存器,其他暫存器右移一位,故四位元的 PO 是 0001 •

前面四個小節所介紹的移位暫存器架構都是屬於右移型的,如果 將接線反接,就可以得出左移型的移位暫存器。當移位暫存器的位元 數目需要增加時,則只需要再多串接正反器即可。此外,這些移位暫 存器都是以正緣觸發 **D**型正反器建構而成,若有需要,讀者可將它們 修改成負緣觸發的移位暫存器。

Copyright©滄海書局